Akim Demaille Étienne Renault Roland Levillain first.last@lrde.epita.fr

EPITA — École Pour l'Informatique et les Techniques Avancées

April 29, 2019

- Intermediate Representations

- 2 Memory Management

- 3 Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

- Intermediate Representations

- Compilers Structure

- Intermediate Representations

- Tree

- 2 Memory Management

- Translation to Intermediate Language

- The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

# Compilers Structure

- Intermediate Representations

- Compilers Structure

- Intermediate Representations

- Tree

- 2 Memory Management

- Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

### So many ends...

#### Ends:

```

front end analysis

middle end generic synthesis

back end specific synthesis

```

```

The gcc team suggests

front end name ("a front end").

front-end adjective ("the front-end interface").

```

#### Front Ends...

The front end is dedicated to analysis:

- lexical analysis (scanning)

- syntactic analysis (parsing)

- ast generation

- static semantic analysis (type checking, context sensitive checks)

- source language specific optimizations

- hir generation

#### ... Back Ends

The back end is dedicated to specific synthesis:

- instruction selection (mir to lir)

- register allocation

- assembly specific optimizations

- assembly code emission

... Middle Ends...

The middle end is dedicated to generic synthesis:

- stepwise refinement of hir to mir

- generic optimizations

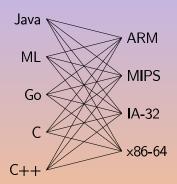

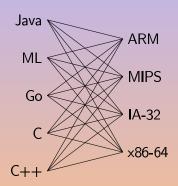

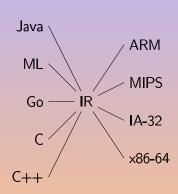

### Retargetable Compilers

### Retargetable Compilers

# Other Compiling Strategies

- Intermediate language-based strategy: SmartEiffel, GHC

- Bytecode strategy: Java bytecode (JVM), CIL (.NET)

- Hybrid approaches: GCJ (Java bytecode or native code)

- Retargetable optimizing back ends: MLRISC, VPO (Very Portable Optimizer), and somehow C-- (Quick C--).

- Modular systems: LLVM (compiler as a library, centered on a typed IR). Contains the LLVM core libraries, Clang, LLDB, etc. Also:

- VMKit: a substrate for virtual machines (JVM, etc.).

- Emscripten: an LLVM-to-JavaScript compiler. Enables C/C++ to JS compilation.

Intermediate Representations (IR) are fundamental.

- Intermediate Representations

- Compilers Structure

- Intermediate Representations

- Tree

- 2 Memory Management

- 3 Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

# Format? Representation? Language?

#### Intermediate representation:

- a faithful model of the source program

- "written" in an abstract language, the intermediate language

- may have an external syntax

- may be interpreted/compiled (havm, byte code)

- may have different levels (gcc's Tree is very much like C).

## What Language Flavor?

- Imperative?

- Stack Based? (Java Byte-code)

- Register Based? (gcc's rtl, tc's Tree)

- Functional? Most functional languages are compiled into a lower level language, eventually a simple  $\lambda$ -calculus.

- Other?

#### What Level?

A whole range of expressivities, typically aiming at making some optimizations easier:

• Keep array expressions?

Yes: adequate for dependency analysis and related optimizations,

No: Good for constant folding, strength reduction, loop invariant code motion, etc.

Keep loop constructs?

What level of machine independence?

Explicit register names?

## Designing an Intermediate Representation

Intermediate-language design is largely an art, not a science.

— [Muchnick, 1997]

```

float a[20][10];

a[i][j+2];

```

```

a[i][j+2];

t1 <- a[i,j+2]

```

float a[20][10];

```

float a[20][10];

. . .

a[i][j+2];

t1 <- a[i,j+2]

t1 < -j + 2

t2 <- i * 20

t3 < -t1 + t2

t4 <- 4 * t3

t5 <- addr a

t6 < - t5 + t4

t7 <- *t6

```

```

float a[20][10];

. . .

a[i][j+2];

t1 <- a[i,j+2]

t1 < -j + 2

r1 < - [fp - 4]

t2 < -i * 20

r2 < -r1 + 2

t3 < -t1 + t2

r3 <- [fp - 8]

t4 <- 4 * t3

r4 <- r3 * 20

t5 <- addr a

r5 <- r4 + r2

t6 < - t5 + t4

r6 <- 4 * r5

t7 <- *t6

r7 <- fp - 216

f1 < - [r7 + r6]

```

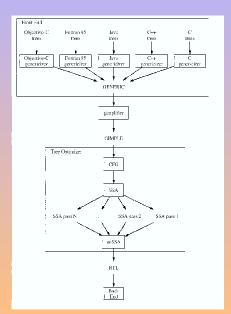

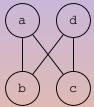

### Different Levels: The GCC Structure

# Stack Based: Java Byte-Code [Edwards, 2003]

```

class Gcd

static public int gcd(int a, int b)

while (a != b)

if (a > b)

a -= b;

else

b -= a:

return a:

static public int main(String[] arg)

return gcd(12, 34);

```

## Stack Based: Java Byte-Code

```

% gcj-3.3 -c gcd.java

17: iload_1

% jcf-dump-3.3 -c gcd

18: iload_0

19: isub

Method name: "gcd" public static

20: istore_1

Signature: 5=(int,int)int

21: goto 0

Attribute "Code", length:66,

24: iload_0

max_stack:2, max_locals:2,

25: ireturn

Attribute "LineNumberTable",

code_length:26

0: iload_0

length: 22, count: 5

1: iload_1

line: 5 at pc: 0

2: if_icmpeq 24

line: 7 at pc: 5

5: iload 0

line: 8 at pc: 10

6: iload 1

line: 10 at pc: 17

7: if_icmple 17

line: 12 at pc: 24

10: iload_0

11: iload_1

12: isub

13: istore 0

```

## Stack Based [Edwards, 2003]

#### Advantages

- Trivial translation of expressions

- Trivial interpreters

- No pressure on registers

- Often compact

#### Disadvantages

- Does not fit with today's architectures

- Hard to analyze

- Hard to optimize

## Stack Based [Edwards, 2003]

#### Advantages

- Trivial translation of expressions

- Trivial interpreters

- No pressure on registers

- Often compact

#### Disadvantages

- Does not fit with today's architectures

- Hard to analyze

- Hard to optimize

#### Stack Based: Examples

ucode, used in hp pa-risk, and mips, was designed for stack evaluation (HP 3000 is stack based).

Today it is less adequate.

mips translates it back and forth to triples for optimization.

hp converts it into sllic (Spectrum Low Level ir) [Muchnick, 1997].

### Register Based: tc's Tree

## Register Based: tc's Tree (1/4)

```

/* == High Level Intermediate representation. == */

# Routine: gcd

label 10

# Prologue

move temp t0 temp fp

move temp fp temp sp

move

temp sp

binop sub temp sp const 12

move

mem temp fp

temp i0

move

mem binop add temp fp const -4

temp i1

move

mem binop add temp fp const -8

temp i2

```

# Register Based: tc's Tree (2/4)

```

# Body

move temp rv

eseq

seq

1abe1 12

cjump ne mem binop add temp fp const -4

mem binop add temp fp const -8

name | 3 name | 1

1abel 13

seq

cjump gt mem binop add temp fp const -4

mem binop add temp fp const -8

name 14 name 15

label 4

move mem binop add temp fp const -4

binop sub mem binop add temp fp const -4

mem binop add temp fp const -8

jump name 16

```

## Register Based: tc's Tree (3/4)

```

label 15

move mem binop add temp fp const -8

binop sub mem binop add temp fp const -8

mem binop add temp fp const -4

label 16

seq end

jump name 12

label 11

seq end

mem binop add temp fp const -4

# Epilogue

move temp sp temp fp

move temp fp temp t0

label end

```

# Register Based: tc's Tree (4/4)

```

# Routine: main

label main

# Prologue

# Body

seq

sxp

call

name print_int

call name 10 temp fp const 42 const 51

call end

call end

sxp

const 0

seq end

# Epilogue

label end

```

How is the structure coded?

Addresses Expressions and instructions have names, or (absolute) addresses. (Stack based is a bit like a relative address).

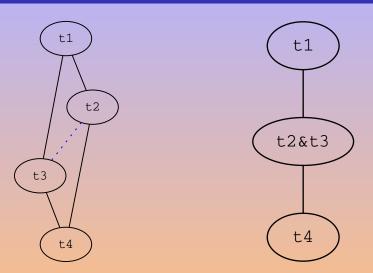

- 2 address instructions? (*triples*)

- 3 address instructions? (quadruples)

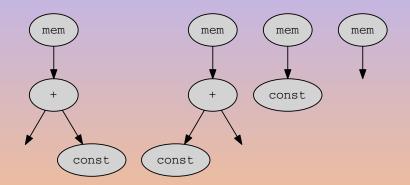

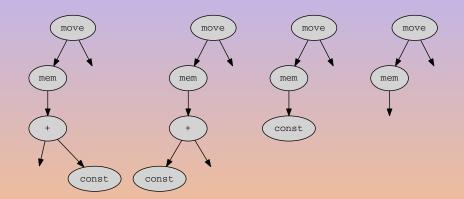

- Tree Expressions and instructions are unnamed, related to each other

- as nodes of trees

- dag Compact, good for local value numbering, but that's all.

How is the structure coded?

Addresses Expressions and instructions have names, or (absolute) addresses. (Stack based is a bit like a relative address).

- 2 address instructions? (triples)

- 3 address instructions? (quadruples)

Tree Expressions and instructions are unnamed, related to each other as nodes of trees

dag Compact, good for local value numbering, but that's all.

#### How is the structure coded?

- Addresses Expressions and instructions have names, or (absolute) addresses. (Stack based is a bit like a relative address).

- 2 address instructions? (triples)

- 3 address instructions? (quadruples)

- Tree Expressions and instructions are unnamed, related to each other as nodes of trees

- dag Compact, good for local value numbering, but that's all.

#### How is the structure coded?

- Addresses Expressions and instructions have names, or (absolute) addresses. (Stack based is a bit like a relative address).

- 2 address instructions? (triples)

- 3 address instructions? (quadruples)

- Tree Expressions and instructions are unnamed, related to each other as nodes of trees

- dag Compact, good for local value numbering, but that's all.

#### How is the structure coded?

- Addresses Expressions and instructions have names, or (absolute) addresses. (Stack based is a bit like a relative address).

- 2 address instructions? (triples)

- 3 address instructions? (quadruples)

- Tree Expressions and instructions are unnamed, related to each other as nodes of trees

- dag Compact, good for local value numbering, but that's all.

# Quadruples vs. Triples [Muchnick, 1997]

```

L1: i <- i + 1

(2) i sto

t1 <- i + 1

(3) i + 1

t2 <- p + 4

(4) p + 4

t3 <- *t2

(5) *(4)

p <- t2

(6) p sto

t4 <- t1 < 10

(7) (3) <

*r <- t3

if t4 goto L1

(9) if (7)

```

# Quadruples vs. Triples [Muchnick, 1997]

# Register Based: gcc's rtl

```

int

gcd(int a, int b)

while (a != b)

if (a > b)

a -= b;

else

b -= a;

return a;

```

### Register Based: gcc's rtl

```

(jump_insn 15 14 16 (set (pc)

(if_then_else (ne (reg:CCZ 17 flags)

(const_int 0 [0x0])

(label_ref 18)

(pc))) -1 (nil)

(nil))

(jump_insn 16 15 17 (set (pc)

(label ref 44)) -1 (nil)

(nil))

(barrier 17 16 18)

(code label 18 17 19 4 "" "" [0 uses])

(note 19 18 20 NOTE_INSN_LOOP_END_TOP_COND)

(note 20 19 21 NOTE_INSN_DELETED)

(note 21 20 22 NOTE INSN DELETED)

```

```

(note 22 21 25 ("gcd.c") 6)

(insn 25 22 26 (set (reg:SI 60)

(mem/f:SI (reg/f:SI 53 virtual-incoming-args) [0 a+0 S4 A32]))

-1 (nil) (nil))

(insn 26 25 27 (set (reg:CCGC 17 flags)

(compare:CCGC (reg:SI 60)

(mem/f:SI (plus:SI (reg/f:SI 53 virtual-incoming-args)

(const_int 4 [0x4])) [0 b+0 S4 A32]))) -1 (nil)

(nil))

(jump_insn 27 26 28 (set (pc)

(if_then_else (le (reg:CCGC 17 flags)

(const_int 0 [0x0]))

(label_ref 34)

(pc))) -1 (nil)

(nil))

```

```

(note 28 27 30 ("gcd.c") 7)

(insn 30 28 31 (set (reg:SI 61)

(mem/f:SI (plus:SI (reg/f:SI 53 virtual-incoming-args)

(const_int 4 [0x4])) [0 b+0 S4 A32])) -1 (nil)

(nil))

(insn 31 30 32 (parallel[

(set (mem/f:SI (reg/f:SI 53 virtual-incoming-args)

[0 a+0 S4 A32])

(minus:SI (mem/f:SI (reg/f:SI 53 virtual-incoming-args)

[0 a+0 S4 A32])

(reg:SI 61)))

(clobber (reg:CC 17 flags))

] ) -1 (nil)

(expr_list:REG_EQUAL (minus:SI (mem/f:SI (reg/f:SI 53

virtual-incoming-args) [0 a+0 S4 A32])

(mem/f:SI (plus:SI (reg/f:SI 53 virtual-incoming-args)

(const_int 4 [0x4])) [0 b+0 S4 A32]))

(nil)))

(jump_insn 32 31 33 (set (pc)

(label_ref 39)) -1 (nil)

(nil))

(barrier 33 32 34)

(code_label 34 33 35 5 "" "" [0 uses])

```

```

(note 35 34 37 ("gcd.c") 9)

(insn 37 35 38 (set (reg:SI 62)

(mem/f:SI (reg/f:SI 53 virtual-incoming-args) [0 a+0 S4 A32]))

-1 (nil) (nil))

(insn 38 37 39 (parallel[

(set (mem/f:SI (plus:SI (reg/f:SI 53 virtual-incoming-args)

(const_int 4 [0x4])) [0 b+0 S4 A32])

(minus:SI (mem/f:SI (plus:SI (reg/f:SI 53

virtual-incoming-args)

(const_int 4 [0x4])) [0 b+0 S4 A32])

(reg:SI 62)))

(clobber (reg:CC 17 flags))

1) -1 (nil)

(expr_list:REG_EQUAL (minus:SI (mem/f:SI (plus:SI (reg/f:SI

53 virtual-incoming-args)

(const_int 4 [0x4])) [0 b+0 S4 A32])

(mem/f:SI (reg/f:SI 53 virtual-incoming-args) [0 a+0 S4 A32]))

(nil)))

(code_label 39 38 41 6 "" "" [0 uses])

(jump_insn 41 39 42 (set (pc)

(label ref 10)) -1 (nil)

(nil))

(barrier 42 41 43)

(note 43 42 44 NOTE_INSN_LOOP_END)

```

```

(note 45 44 46 ("gcd.c") 11)

(note 46 45 47 NOTE_INSN_DELETED)

(note 47 46 49 NOTE_INSN_DELETED)

(insn 49 47 51 (set (reg:SI 64)

(mem/f:SI (reg/f:SI 53 virtual-incoming-args) [0 a+0 S4 A32])) -1 (nil)

(nil))

(insn 51 49 52 (set (reg:SI 58)

(reg:SI 64)) -1 (nil)

(nil))

(jump_insn 52 51 53 (set (pc)

(label_ref 56)) -1 (nil)

(nil))

(barrier 53 52 54)

(note 54 53 55 NOTE_INSN_FUNCTION_END)

(note 55 54 59 ("gcd.c") 12)

(insn 59 55 60 (clobber (reg/i:SI 0 eax)) -1 (nil)

(nil))

(insn 60 59 56 (clobber (reg:SI 58)) -1 (nil)

(nil))

(code_label 56 60 58 1 "" "" [0 uses])

(insn 58 56 61 (set (reg/i:SI 0 eax)

(reg:SI 58)) -1 (nil)

(nil))

(insn 61 58 0 (use (reg/i:SI 0 eax)) -1 (nil)

```

# Register Based [Edwards, 2003]

#### Advantages

- Suits today's architectures

- Clearer data flow

#### Disadvantages

- Harder to synthesize

- Less compact

- Harder to interpret

# Register Based [Edwards, 2003]

#### Advantages

- Suits today's architectures

- Clearer data flow

#### Disadvantages

- Harder to synthesize

- Less compact

- Harder to interpret

#### Tree

- Intermediate Representations

- Compilers Structure

- Intermediate Representations

- Tree

- 2 Memory Management

- Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

# Tree [Appel, 1998]

A simple intermediate language:

- Tree structure (no kidding...)

- Unbounded number of registers (temporaries)

- Two way conditional jump

#### Tree: Grammar

```

\langle \text{Exp} \rangle ::= \text{"const"} \text{ int}

"name" (Label)

"temp" (Temp)

"binop" (Oper) (Exp) (Exp)

"mem" (Exp)

"call" \langle \text{Exp} \rangle [{\langle \text{Exp} \rangle}] "call end"

"eseq" (Stm) (Exp)

\langle Stm \rangle ::= "move" \langle Exp \rangle \langle Exp \rangle

"sxp" (Exp)

| "jump" \langle Exp \rangle [{\langle Label \rangle}]

"cjump" (Relop) (Exp) (Exp) (Label) (Label)

"seq" [{\langle Stm \rangle}] "seq end"

"label" (Label)

(Oper) ::= "add" | "sub" | "mul" | "div" | "mod"

⟨Relop⟩ ::= "eq" | "ne" | "lt" | "gt" | "le" | "ge"

```

### Tree Samples

```

\% echo '1 + 2 * 3' | tc -H -

/* == High Level Intermediate representation. == */

# Routine: Main Program

label Main

# Prologue

# Body

sxp

binop add

const 1

binop mul

const 2

const 3

# Epilogue

label end

```

### Tree Samples

```

% echo 'if 1 then print_int (1)' | tc -H -

# Routine: Main Program

label Main

# Prologue

# Body

seq

cjump ne, const 1, const 0, name 11, name 12

label 11

sxp call name print_int, const 1

jump name 13

label 12

sxp const 0

label 13

seq end

# Epilogue

label end

```

# Memory Management

- Intermediate Representations

- 2 Memory Management

- Memory Management

- Activation Blocks

- Nonlocal Variables

- Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

# Memory Management

- Intermediate Representations

- 2 Memory Management

- Memory Management

- Activation Blocks

- Nonlocal Variables

- Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

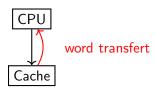

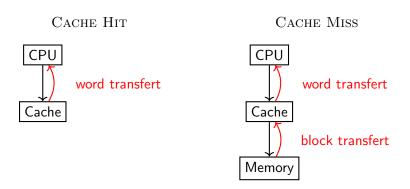

# Memory Hierarchy [Appel, 1998]

Different kinds of memory in a computer, with different performances:

Registers Small memory units built on the cpu (bytes, 1 cycle)

L1 Cache Last main memory access results (kB, 2-3 cycles)

L2 Cache (MB, 10 cycles)

Memory The usual ram (GB, 100 cycles)

Storage Disks (100GB, TB, > 1Mcycles)

Use the registers as much as possible.

### Register Overflow

What if there are not enough registers? Use the main memory, but how? Recursion:

Without Each name is bound once. It can be statically allocated a single unit of main memory. (Cobol, Concurrent Pascal, Fortran (unless recursive)).

With A single name can be part of several concurrent bindings.

Memory allocation must be dynamic.

### Register Overflow

What if there are not enough registers? Use the main memory, but how? Recursion:

- Without Each name is bound once. It can be statically allocated a single unit of main memory. (Cobol, Concurrent Pascal, Fortran (unless recursive)).

- With A single name can be part of several concurrent bindings.

Memory allocation must be dynamic.

Depending on the persistence, several models:

Global Global objects, whose liveness is equal to that of the program, are statically allocated (e.g., static variables in C)

Automatic Liveness is bound to that of the host function (e.g., auto variables in C)

Heap Liveness is independent of function liveness:

Garbage Collected

With or without new

(12 m. Completelle MT)

(lisp, Smalltalk, ML, Haskell, Tiger, Perl etc.

Depending on the persistence, several models:

Global Global objects, whose liveness is equal to that of the program, are statically allocated (e.g., static variables in C)

Automatic Liveness is bound to that of the host function (e.g., auto variables in C)

Heap Liveness is independent of function liveness:

- Garbage Collected

- With or without new

- VIIII OF WITHOUT HEW

- (lisp, Smalltalk, ML, Haskell, Tiger, Perl etc.).

Depending on the persistence, several models:

```

Global Global objects, whose liveness is equal to that of the program, are statically allocated (e.g., static variables in C)

```

Automatic Liveness is bound to that of the host function (e.g., auto variables in C)

Heap Liveness is independent of function liveness:

```

User Controlled

malloc/free (C), new/dispose (Pascal),

new/delete (C++) etc.

Garbage Collected

With or without new

(lisp, Smalltalk, ML, Haskell, Tiger, Perl etc.)

```

```

Depending on the persistence, several models:

Global Global objects, whose liveness is equal to that of the program,

are statically allocated

(e.g., static variables in C)

Automatic Liveness is bound to that of the host function

(e.g., auto variables in C)

Heap Liveness is independent of function liveness:

User Controlled

malloc/free (C), new/dispose (Pascal),

new/delete (C++) etc.

```

```

Depending on the persistence, several models:

Global Global objects, whose liveness is equal to that of the program,

are statically allocated

(e.g., static variables in C)

Automatic Liveness is bound to that of the host function

(e.g., auto variables in C)

Heap Liveness is independent of function liveness:

User Controlled

malloc/free (C), new/dispose (Pascal),

new/delete (C++) etc.

Garbage Collected

With or without new

(lisp, Smalltalk, ML, Haskell, Tiger, Perl etc.).

```

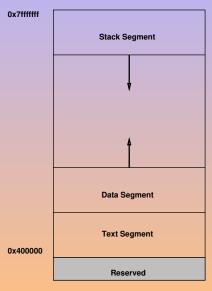

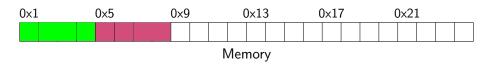

# spim Memory Model [Larus, 1990]

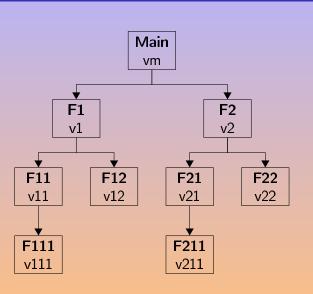

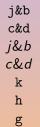

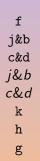

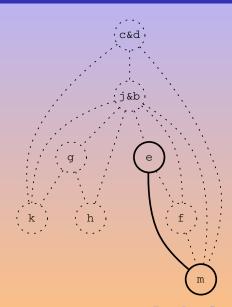

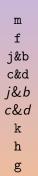

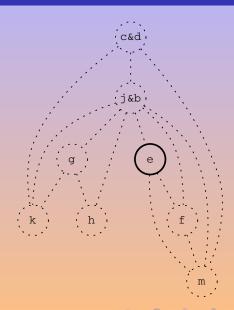

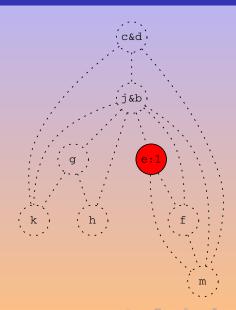

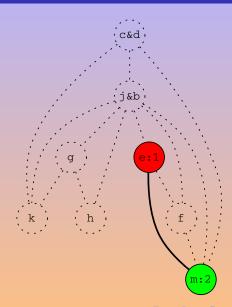

### Stack Management

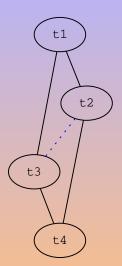

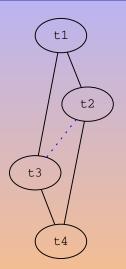

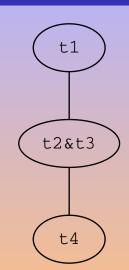

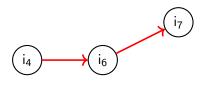

Function calls is a last-in first-out process, hence, it is properly represented by a stack.

Or...

"Call tree": the complete history of calls.

The execution of the program is its depth first traversal.

Depth-first walk requires a stack.

- Intermediate Representations

- 2 Memory Management

- Memory Management

- Activation Blocks

- Nonlocal Variables

- Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

- In recursive languages, a single routine can be "opened" several times concurrently.

- An activation designates one single instance of execution.

- Automatic variables are bound to the liveness of the activation.

- Their location is naturally called activation block, or stack frame.

- In recursive languages, a single routine can be "opened" several times concurrently.

- An activation designates one single instance of execution.

- Automatic variables are bound to the liveness of the activation.

- Their location is naturally called *activation block*, or *stack frame*.

- In recursive languages, a single routine can be "opened" several times concurrently.

- An activation designates one single instance of execution.

- Automatic variables are bound to the liveness of the activation.

- Their location is naturally called activation block, or stack frame.

- In recursive languages, a single routine can be "opened" several times concurrently.

- An activation designates one single instance of execution.

- Automatic variables are bound to the liveness of the activation.

- Their location is naturally called activation block, or stack frame.

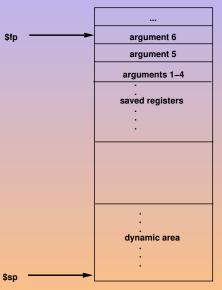

#### Activation Blocks Contents

Data to store on the stack:

arguments incoming

local variables user automatic variables

return address where to return

saved registers the caller's environment to restore

temp compiler automatic variables, spills

static link when needed

#### Activation Blocks Layout

The layout is suggested by the constructor. Usually the layout is from earliest known, to latest.

# Activation Blocks Layout on mips [Larus, 1990]

#### Frame & Stack Pointers

The stack of activation blocks is implemented as an array with frame pointer the inner frontier of the activation block stack pointer the outer frontier

Usually the stack is represented growing towards the bottom.

# Flexible Automatic Memory

```

auto Static size, automatic memory.

malloc Dynamic size, persistent memory.

Automatic memory is extremely convenient...

int

open2(char* str1, char* str2, int flags, int mode)

{

char name[strlen(str1) + strlen(str2) + 1];

stpcpy(stpcpy(name, str1), str2);

return open(name, flags, mode);

}

```

## Flexible Automatic Memory

malloc is a poor replacement.

```

int

open2(char* str1, char* str2, int flags, int mode)

₹

char* name

= (char*) malloc(strlen(str1) + strlen(str2) + 1);

if (name == 0)

fatal("virtual memory exceeded");

stpcpy(stpcpy(name, str1), str2);

int fd = open(name, flags, mode);

free(name):

return fd;

```

## Flexible Automatic Memory

alloca is a good replacement.

# Advantages of alloca [Loosemore et al., 2003]

- Using alloca wastes very little space and is very fast.

(It is open-coded by the GNU C compiler.)

- alloca does not cause memory fragmentation.

Since alloca does not have separate pools for different sizes of block, space used for any size block can be reused for any other size.

- Automatically freed.

Nonlocal exits done with longjmp automatically free the space allocated with alloca when they exit through the function that called alloca. This is the most important reason to use alloca.

## Advantages of alloca [Loosemore et al., 2003]

- Using alloca wastes very little space and is very fast.

(It is open-coded by the GNU C compiler.)

- alloca does not cause memory fragmentation.

Since alloca does not have separate pools for different sizes of block, space used for any size block can be reused for any other size.

- Automatically freed.

Nonlocal exits done with longjmp automatically free the space allocated with alloca when they exit through the function that called alloca. This is the most important reason to use alloca.

# Advantages of alloca [Loosemore et al., 2003]

- Using alloca wastes very little space and is very fast.

(It is open-coded by the GNU C compiler.)

- alloca does not cause memory fragmentation.

Since alloca does not have separate pools for different sizes of block, space used for any size block can be reused for any other size.

- Automatically freed.

Nonlocal exits done with longjmp automatically free the space allocated with alloca when they exit through the function that called alloca. This is the most important reason to use alloca.

## Disadvantages of alloca [Loosemore et al., 2003]

- If you try to allocate more memory than the machine can provide, you

don't get a clean error message.

Instead you get a fatal signal like the one you would get from an

infinite recursion; probably a segmentation violation.

- Some non-GNU systems fail to support alloca, so it is less portable However, a slower emulation of alloca written in C is available for use on systems with this deficiency.

## Disadvantages of alloca [Loosemore et al., 2003]

- If you try to allocate more memory than the machine can provide, you

don't get a clean error message.

Instead you get a fatal signal like the one you would get from an

infinite recursion; probably a segmentation violation.

- Some non-GNU systems fail to support alloca, so it is less portable. However, a slower emulation of alloca written in C is available for use on systems with this deficiency.

# Arrays vs. Alloca [Loosemore et al., 2003]

- A variable size array's space is freed at the end of the scope of the name of the array.

The space allocated with alloca remains until the end of the function.

- It is possible to use alloca within a loop, allocating an additional block on each iteration.

This is impossible with variable sized arrays.

# Arrays vs. Alloca [Loosemore et al., 2003]

- A variable size array's space is freed at the end of the scope of the name of the array.

The space allocated with alloca remains until the end of the function.

- It is possible to use alloca within a loop, allocating an additional block on each iteration.

- This is impossible with variable-sized arrays.

## Implementing Dynamic Arrays & Alloca

- Playing with \$sp which makes \$fp mandatory.

- An additional stack (as with the C emulation of alloca).

### Nonlocal Variables

- Intermediate Representations

- 2 Memory Management

- Memory Management

- Activation Blocks

- Nonlocal Variables

- Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

### escapes-n-recursion

```

let function trace(fn: string, val: int) =

(print(fn); print("("); print_int(val); print(") "))

function one(input : int) =

let function two() =

(trace("two", input); one(input - 1))

in

if input > 0 then

(two(); trace("one", input))

end

in

one(3); print("\n")

end

```

### escapes-n-recursion

```

let function trace(fn: string, val: int) =

(print(fn); print("("); print_int(val); print(") "))

function one(input : int) =

let function two() =

(trace("two", input); one(input - 1))

in

if input > 0 then

(two(); trace("one", input))

end

in

one(3); print("\n")

end

% tc -H escapes-n-recursion.tig > f.hir && havm f.hir

```

### escapes-n-recursion

```

let function trace(fn: string, val: int) =

(print(fn); print("("); print_int(val); print(") "))

function one(input : int) =

let function two() =

(trace("two", input); one(input - 1))

in

if input > 0 then

(two(); trace("one", input))

end

in

one(3); print("\n")

end

% tc -H escapes-n-recursion.tig > f.hir && havm f.hir

two(3) two(2) two(1) one(1) one(2) one(3)

```

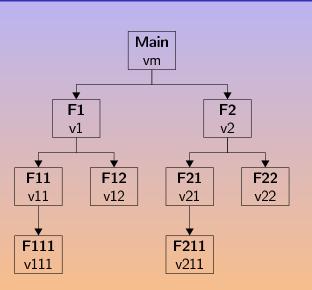

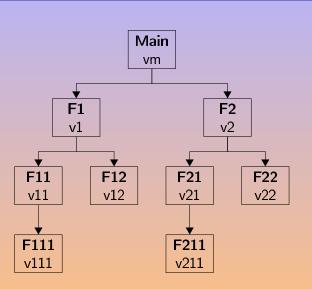

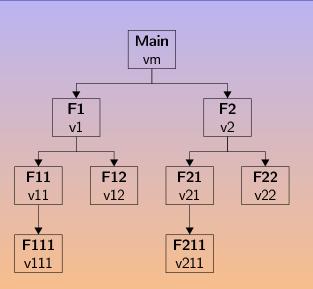

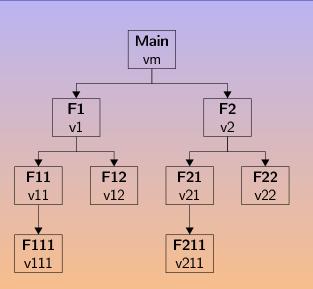

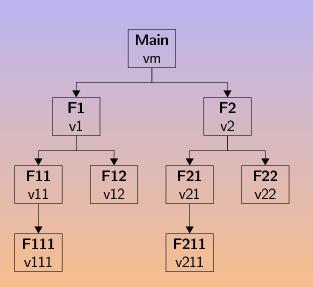

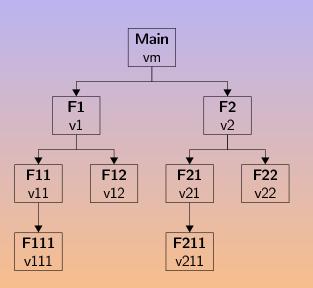

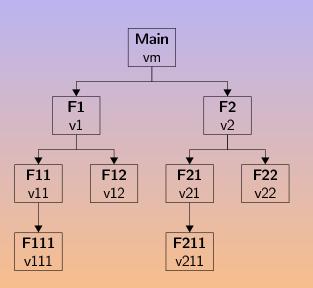

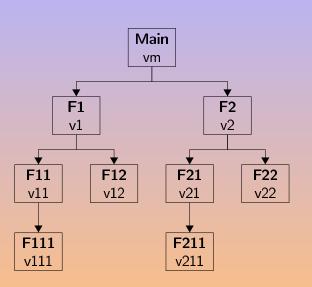

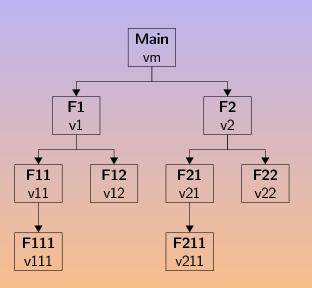

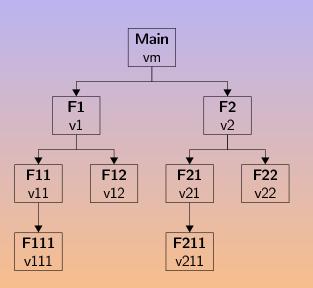

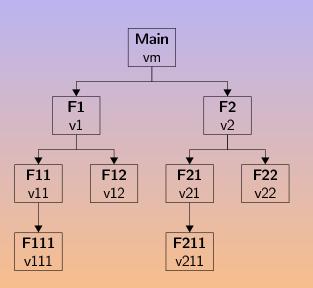

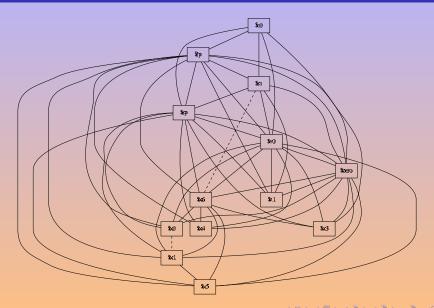

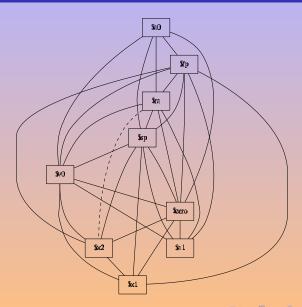

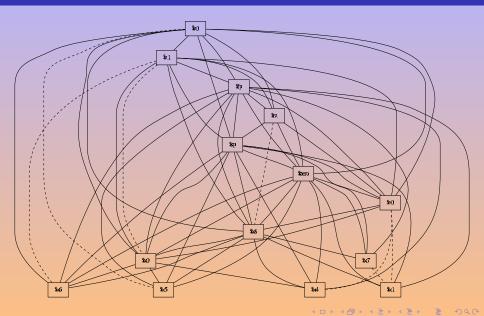

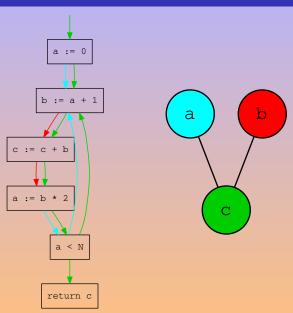

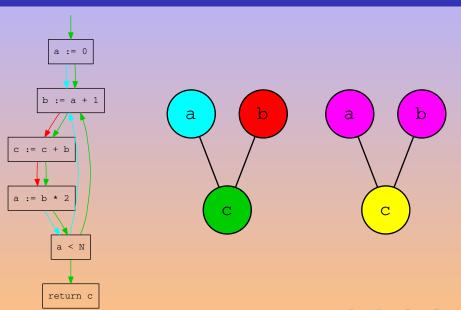

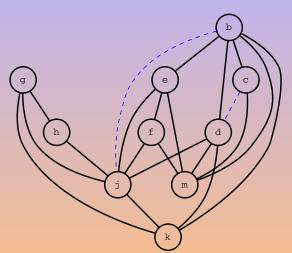

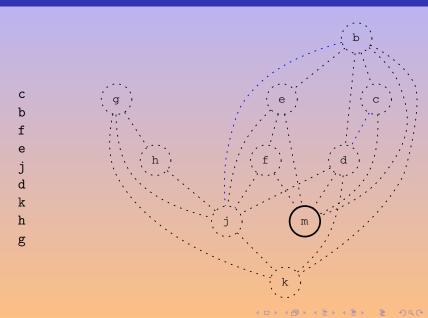

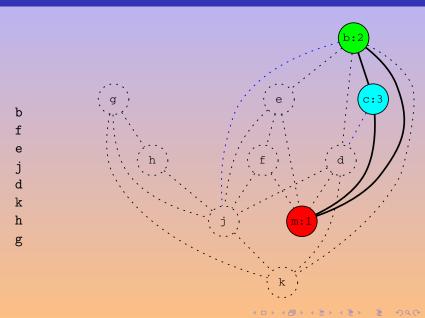

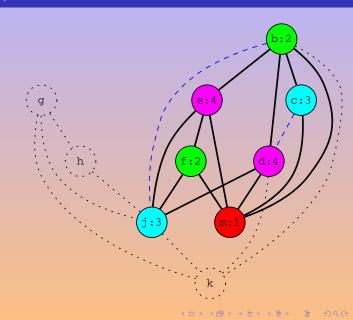

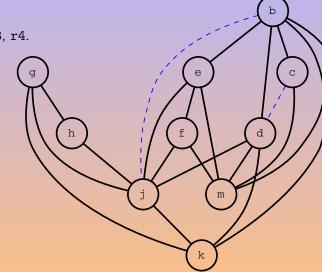

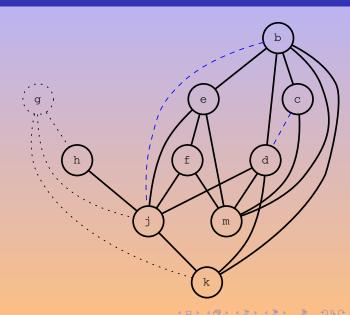

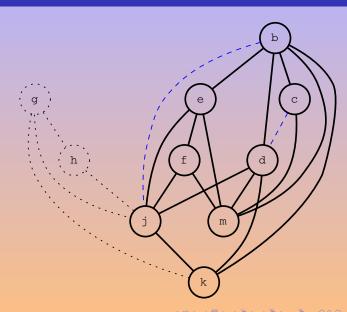

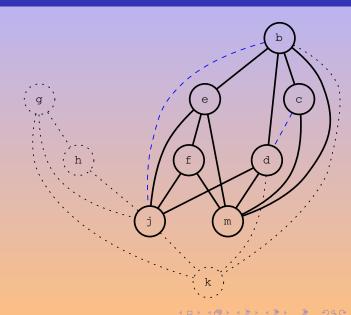

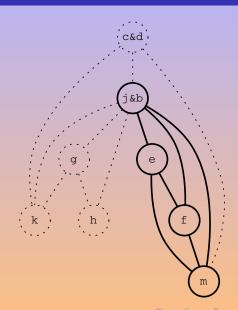

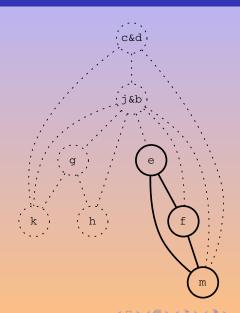

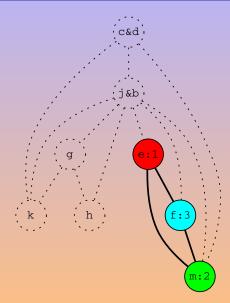

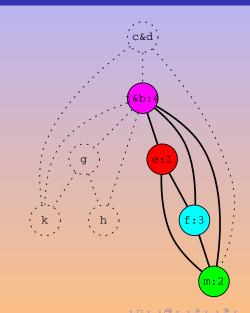

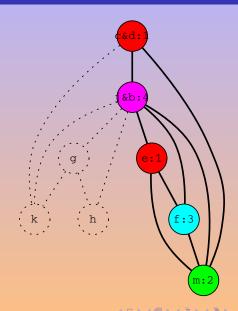

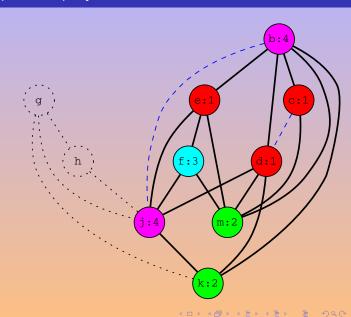

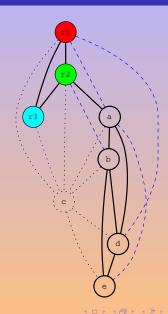

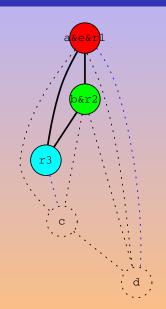

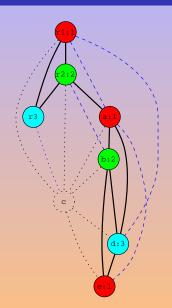

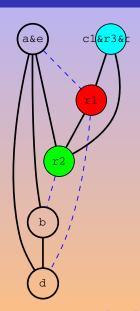

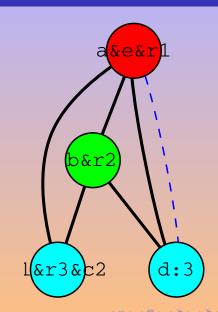

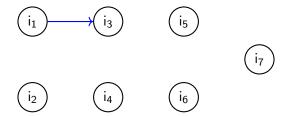

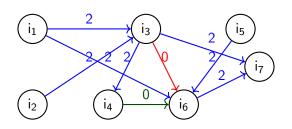

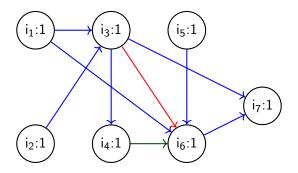

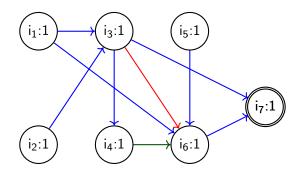

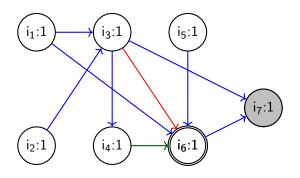

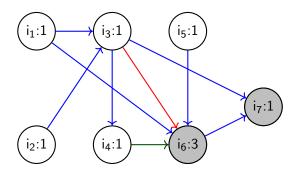

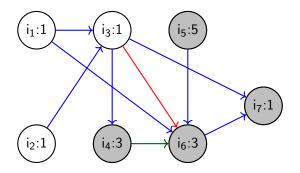

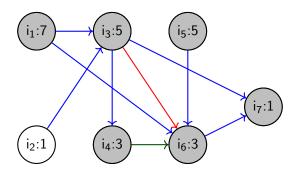

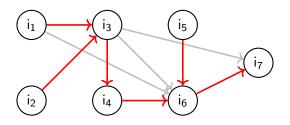

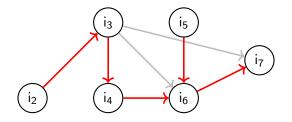

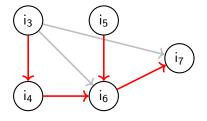

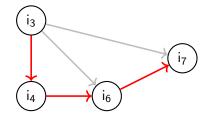

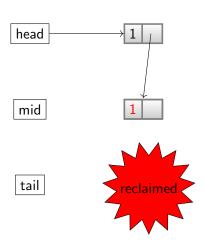

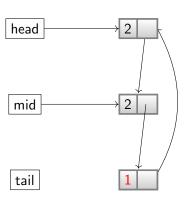

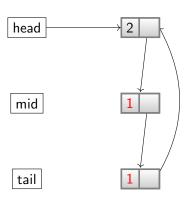

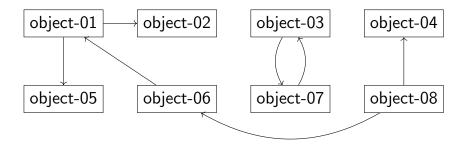

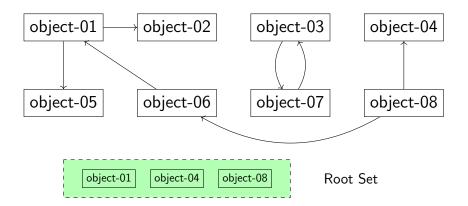

- Main uses vm

- Main calls F1

- F1 uses v1

- F1 uses vm, nor

- 5 F1 calls F11

- **6** F11 uses v11

- F11 uses v1

- 6 F11 uses vm

- F11 calls F12

- U F12 Calls F1

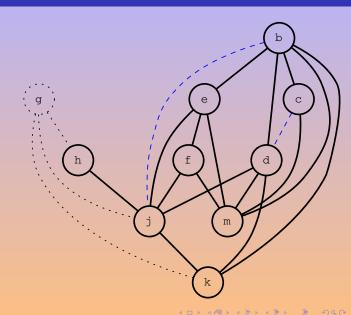

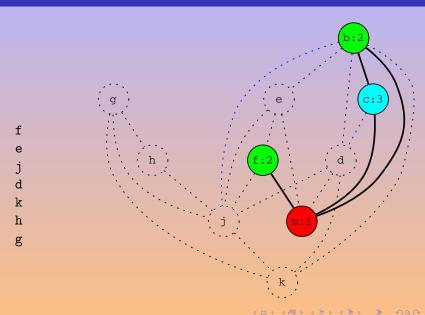

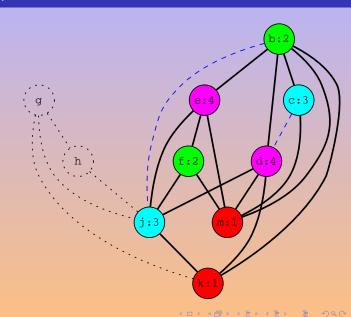

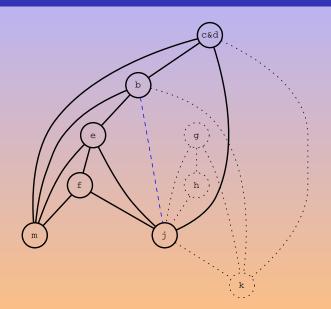

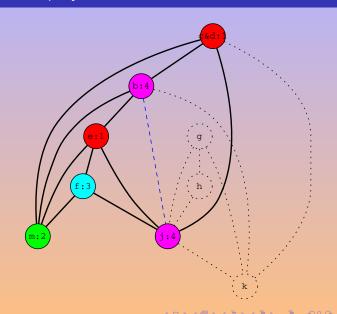

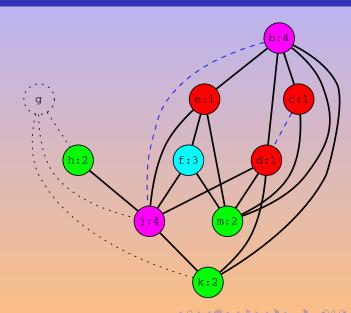

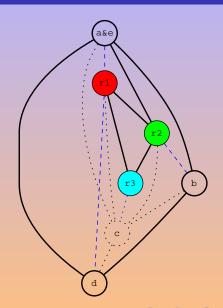

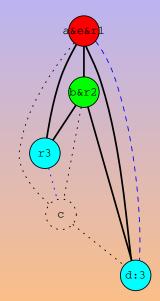

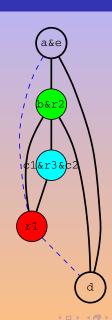

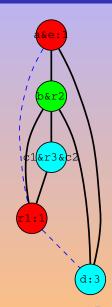

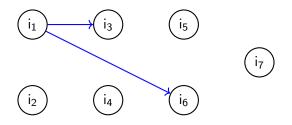

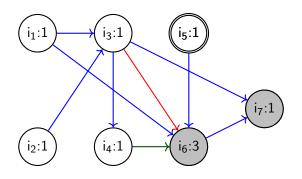

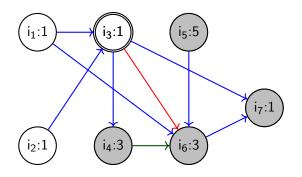

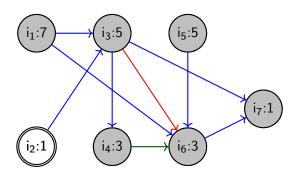

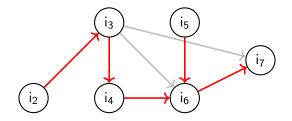

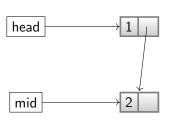

- Main uses vm

- Main calls F1

- 3 F1 uses v1

- local

- F1 calls F11F11 uses v11

- F11 uses v1

- **3** F11 uses vm

- F11 calls F12

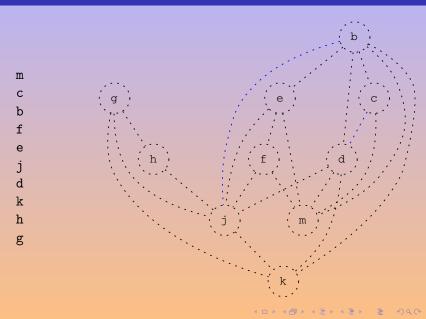

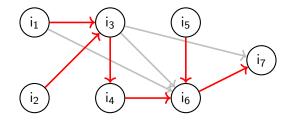

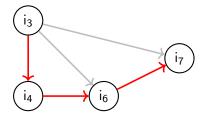

- Main uses vm

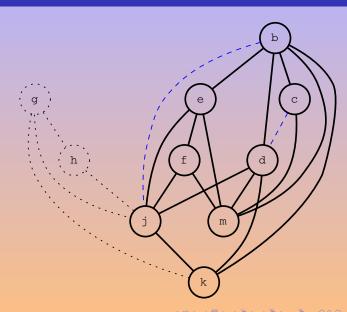

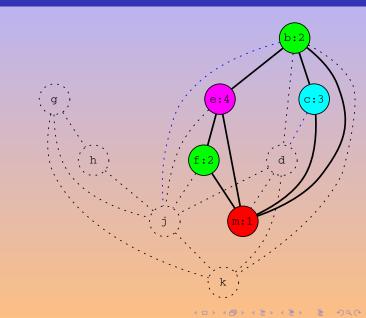

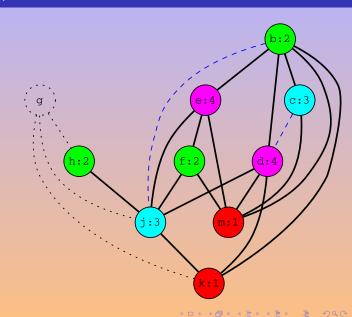

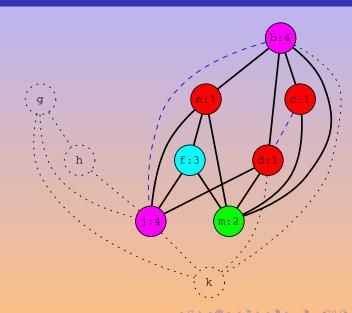

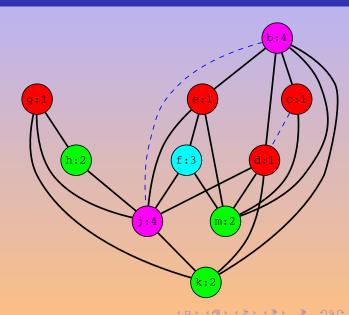

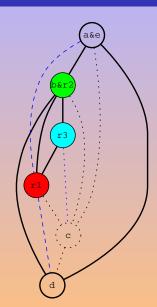

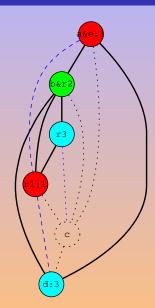

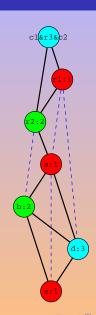

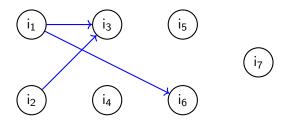

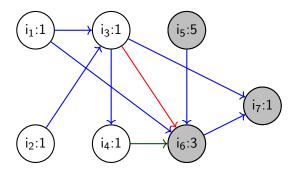

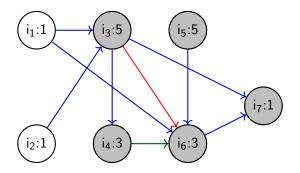

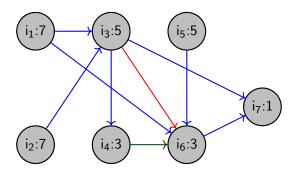

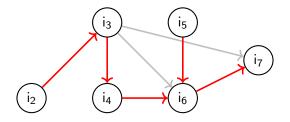

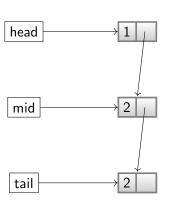

- 2 Main calls F1

- F1 uses v1

- 4 F1 uses vm, non local

- 5 F1 calls F11

- **6** F11 uses v11

- F11 uses v1

- **6** F11 uses vm

- F11 calls F12

- F12 calls F1

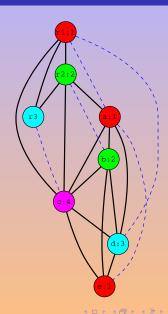

- Main uses vm

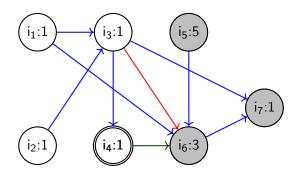

- Main calls F1

- F1 uses v1

- F1 uses vm, non

local

- 5 F1 calls F11

- F11 uses v11

- **7** F11 uses v1

- F11 uses vm

- F11 calls F12

- F12 calls F1

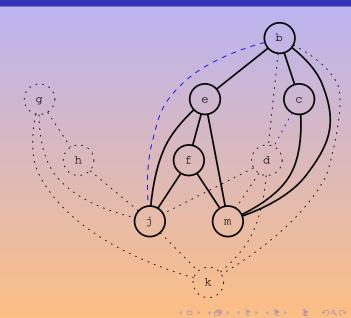

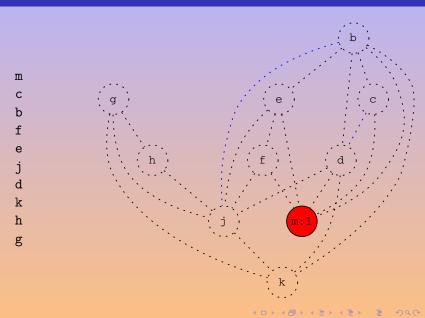

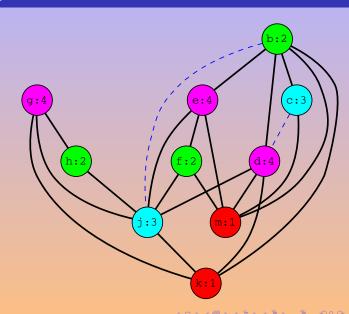

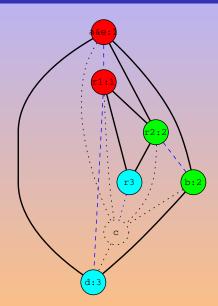

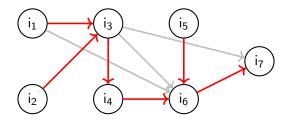

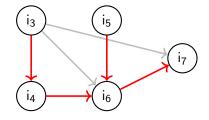

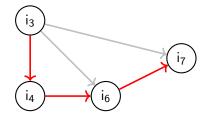

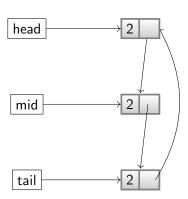

- Main uses vm

- Main calls F1

- 3 F1 uses v1

- 4 F1 uses vm, non local

- 5 F1 calls F11

- 9 F11 uses --1

- F11 uses tm

- F11 calls F19

- FII CallS F12

- F12 calls F1

- Main uses vm

- Main calls F1

- 3 F1 uses v1

- 4 F1 uses vm, non local

- F1 calls F11

- **5** F11 uses v11

- F11 uses v1

- 6 F11 uses vm

- F11 calls F12

- F12 calls F1

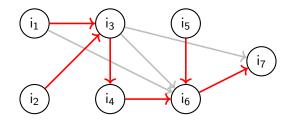

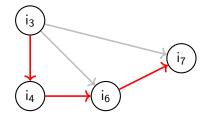

- Main uses vm

- Main calls F1

- 3 F1 uses v1

- F1 uses vm, non local

- F1 calls F11

- **o** F11 uses v11

- F11 uses v1

- F11 uses vm

- F11 calls F12

- F12 calls F1

- Main uses vm

- Main calls F1

- F1 uses v1

- F1 uses vm, non local

- F1 calls F11

- **o** F11 uses v11

- F11 uses v1

- F11 uses vm

- F11 calls F12

- F12 calls F1

- Main uses vm

- Main calls F1

- 3 F1 uses v1

- F1 uses vm, non local

- F1 calls F11

- **o** F11 uses v11

- F11 uses v1

- F11 uses vm

- F11 calls F12

- F12 calls F1

- Main uses vm

- Main calls F1

- 3 F1 uses v1

- F1 uses vm, non local

- F1 calls F11

- **6** F11 uses v11

- F11 uses v1

- 3 F11 uses vm

- F11 calls F12

- F12 calls F1

- Main uses vm

- Main calls F1

- 3 F1 uses v1

- F1 uses vm, non local

- F1 calls F11

- **o** F11 uses v11

- F11 uses v1

- 3 F11 uses vm

- F11 calls F12

- F12 calls F1

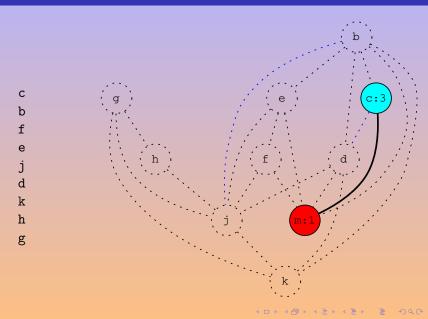

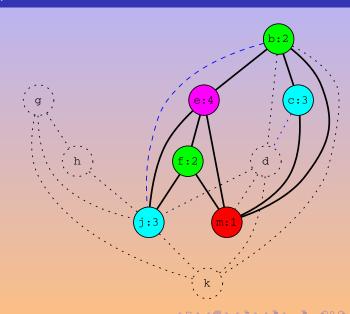

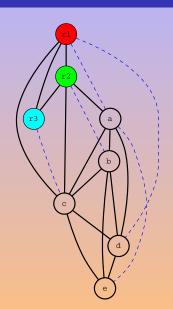

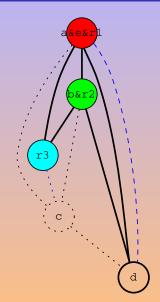

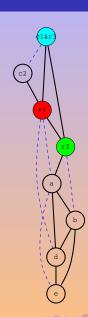

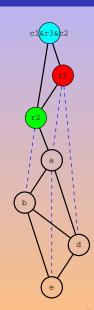

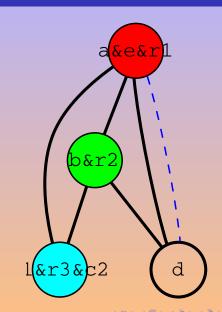

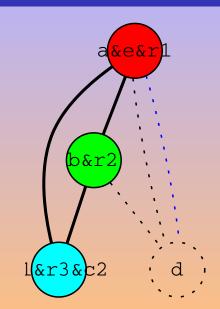

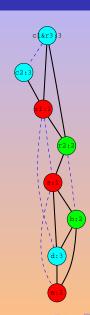

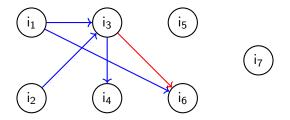

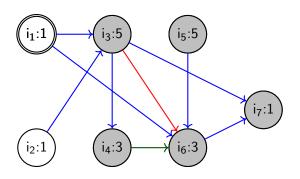

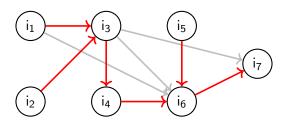

The caller must provide the callee with its static link.

| Caller | Callee | Static Link                                           |

|--------|--------|-------------------------------------------------------|

| Main   | F1     | $fp_{Main} = fp$                                      |

| F1     | F11    | $fp_{F1} = fp$                                        |

| F11    | F12    | $fp_{F1} = sl_{F11} = *fp_{F11} = *fp$                |

| F12    | F2     | $fp_{Main} = sl_{F1} = *sl_{F12} = **fp_{F12} = **fp$ |

| F2     | F22    | $fp_{F2} = fp$                                        |

| F22    | F11    | fp <sub>F1</sub> = ???                                |

Assuming that the static link is stored at fp.

## Higher Order Functions

```

let

function addgen (a: int) : int -> int =

let.

function res (b: int) : int =

a + b

in

res

end

var add50 := addgen (50)

in

add50 (1)

end

```

# Translation to Intermediate Language

- Intermediate Representations

- 2 Memory Management

- 3 Translation to Intermediate Language

- Calling Conventions

- Clever Translations

- Complex Expressions

- 4 The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

# Calling Conventions

- Intermediate Representations

- 2 Memory Management

- 3 Translation to Intermediate Language

- Calling Conventions

- Clever Translations

- Complex Expressions

- The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

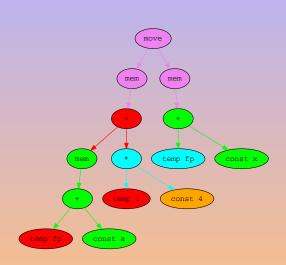

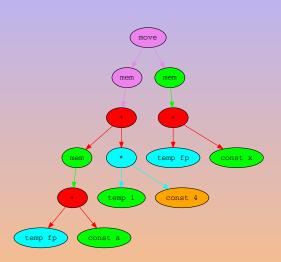

## Calling Conventions at hir Level

#### You must:

- Preserve some registers (fp, sp)

- Allocate the frame

- Handle the static link (i0)

- Receive the (other) arguments (i1, i2...)

#### You don't:

- Save temporaries (havm has magic for recursion)

- Jump to the ra (this is not nice feature from havm)

## havm Calling Conventions

```

let function gcd (a: int, b: int) : int = (...)

in print_int (gcd (42, 51)) end

# Routine: gcd

# Body

label 10

move temp rv

# Prologue

eseq

move temp t2, temp fp

move temp fp, temp sp

temp t0

# Epilogue

move temp sp, temp sp - const 4

move mem temp fp, temp i0

move temp sp, temp fp

move temp t0, temp i1

move temp fp, temp t2

move temp t1, temp i2

label end

# Routine: Main Program

label Main

sxp call name print_int

call name 10 temp fp

const 42 const 51

label end

◆□ ▶ ◆□ ▶ ◆ ■ ● り へ ○

```

### Clever Translations

- Intermediate Representations

- 2 Memory Management

- 3 Translation to Intermediate Language

- Calling Conventions

- Clever Translations

- Complex Expressions

- The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

What is the right translation for  $\alpha < \beta$ , with  $\alpha$  and  $\beta$  two arbitrary expressions?

```

cjump (\alpha < \beta, ltrue, lfalse)

eseq (seq (cjump (\alpha < \beta, ltrue, lfalse), label ltrue move temp t, const 1 jump lend label lfalse move temp t, const 0 label lend), temp t)

```

What is the right translation for  $\alpha < \beta$ , with  $\alpha$  and  $\beta$  two arbitrary expressions?

```

① cjump (\alpha < \beta, ltrue, lfalse)

```

```

eseq (seq (cjump (\alpha < \beta, ltrue, lfalse), label ltrue move temp t, const 1 jump lend label lfalse move temp t, const 0 label lend), temp t)

```

```

3 seq (sxp (\alpha) sxp (\beta)

```

What is the right translation for  $\alpha < \beta$ , with  $\alpha$  and  $\beta$  two arbitrary expressions?

```

① cjump (\alpha < \beta, ltrue, lfalse)

```

```

eseq (seq (cjump (\alpha < \beta, ltrue, lfalse), label ltrue move temp t, const 1 jump lend label lfalse move temp t, const 0 label lend), temp t)

```

```

3 seq (sxp (\alpha) sxp (\beta)

```

$\bigcirc$  cjump ( $\alpha < \beta$ , ltrue, lfalse)

What is the right translation for  $\alpha < \beta$ , with  $\alpha$  and  $\beta$  two arbitrary expressions?

```

eseq (seq (cjump (\alpha < \beta, ltrue, lfalse), label ltrue move temp t, const 1 jump lend label lfalse move temp t, const 0 label lend),

```

```

3 seq (sxp (\alpha) sxp (\beta))

```

temp t)

What is the right translation for  $\alpha < \beta$ , with  $\alpha$  and  $\beta$  two arbitrary expressions?

```

oldsymbol{0} cjump (lpha < eta, ltrue, lfalse)

```

```

eseq (seq (cjump (\alpha < \beta, ltrue, lfalse), label ltrue move temp t, const 1 jump lend label lfalse move temp t, const 0 label lend), temp t)

```

```

3 seq (sxp (\alpha) sxp (\beta))

```

```

1 if \alpha < \beta then ...

```

What is the right translation for  $\alpha < \beta$ , with  $\alpha$  and  $\beta$  two arbitrary expressions?

```

1 cjump (\alpha < \beta, ltrue, lfalse)

```

```

eseq (seq (cjump (\alpha < \beta, ltrue, lfalse), label ltrue move temp t, const 1 jump lend label lfalse move temp t, const 0 label lend), temp t)

```

```

3 seq (sxp (\alpha) sxp (\beta))

```

```

① if \alpha < \beta then ...

```

- $\mathbf{a} := \alpha < \beta$

- $\bigcirc$  ( $\alpha < \beta$ , ())

What is the right translation for  $\alpha < \beta$ , with  $\alpha$  and  $\beta$  two arbitrary expressions?

```

1 cjump (\alpha < \beta, ltrue, lfalse)

```

```

2 eseq (seq (cjump (\alpha < \beta, ltrue, lfalse), label ltrue move temp t, const 1 jump lend label lfalse move temp t, const 0 label lend), temp t)

```

```

3 seq (sxp (\alpha) sxp (\beta))

```

```

① if \alpha < \beta then ...

```

$$\textbf{2} \text{ a := } \alpha < \beta$$

What is the right translation for  $\alpha < \beta$ , with  $\alpha$  and  $\beta$  two arbitrary expressions?

```

1 cjump (\alpha < \beta, ltrue, lfalse)

```

```

2 eseq (seq (cjump (\alpha < \beta, ltrue, lfalse), label ltrue move temp t, const 1 jump lend label lfalse move temp t, const 0 label lend), temp t)

```

```

3 seq (sxp (\alpha) sxp (\beta))

```

- ① if  $\alpha < \beta$  then ...

- $oldsymbol{2}$  a :=  $\alpha < \beta$

- $\odot$  ( $\alpha < \beta$ , ()).

- The right translation depends upon the use.

This is context sensitive!

- How to implement this?

- Don't forget to preserve the demands of higher levels...

- Eek.

- The right translation depends upon the *use*. This is context sensitive!

- How to implement this?

- When entering an IfExp, warn "I want a condition";

- then, depending whether it is an expression or a statement, warn "I want an expression" or "I want a statement".

- Don't forget to preserve the demands of higher levels...

- Eek.

- The right translation depends upon the *use*. This is context sensitive!

- How to implement this?

- When entering an IfExp, warn "I want a condition",

- then, depending whether it is an expression or a statement, warn "I want an expression" or "I want a statement".

- Don't forget to preserve the demands of higher levels...

- Eek.

- The right translation depends upon the *use*. This is context sensitive!

- How to implement this?

- When entering an IfExp, warn "I want a condition",

- then, depending whether it is an expression or a statement, warn "I want an expression" or "I want a statement".

- Don't forget to preserve the demands of higher levels...

- Eek.

- The right translation depends upon the *use*. This is context sensitive!

- How to implement this?

- When entering an IfExp, warn "I want a condition",

- then, depending whether it is an expression or a statement, warn "I want an expression" or "I want a statement".

- Don't forget to preserve the demands of higher levels...

- Eek.

- The right translation depends upon the *use*. This is context sensitive!

- How to implement this?

- When entering an IfExp, warn "I want a condition",

- then, depending whether it is an expression or a statement, warn "I want an expression" or "I want a statement".

- Don't forget to preserve the demands of higher levels...

- Eek.

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

| Exp       | un_nx  | un_ex | $un_cx(t, f)$ |

|-----------|--------|-------|---------------|

| Ex(e)     | sxp(e) | е     |               |

| Cx(a < b) |        |       |               |

| Nx(s)     |        |       |               |

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

| Exp       | un_nx  | un_ex | $un_cx(t, f)$           |

|-----------|--------|-------|-------------------------|

| Ex(e)     | sxp(e) | e     | cjump(e $\neq$ 0, t, f) |

| Cx(a < b) |        |       |                         |

| N×(s)     |        |       |                         |

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

```

\begin{array}{c|ccccc} Exp & un\_nx & un\_ex & un\_cx \ (t, f) \\ \hline Ex(e) & sxp(e) & e & cjump(e \neq 0, t, f) \\ \hline Cx(a < b) & seq(sxp(a), sxp(b)) \\ \hline Nx(s) & & & & & & & & & \\ \hline \end{array}

```

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

$$\begin{array}{c|ccccc} Exp & un\_nx & un\_ex & un\_cx \ (t, f) \\ \hline Ex(e) & sxp(e) & e & cjump(e \neq 0, t, f) \\ Cx(a < b) & seq(sxp(a), sxp(b)) & eseq(t \leftarrow (a < b), t) \\ Nx(s) & & \end{array}$$

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

| Exp       | un_nx               | un_ex                           | $un_cx(t, f)$           |

|-----------|---------------------|---------------------------------|-------------------------|

| Ex(e)     | sxp(e)              | е                               | cjump(e $\neq$ 0, t, f) |

| Cx(a < b) | seq(sxp(a), sxp(b)) | $eseq(t \leftarrow (a < b), t)$ | cjump(a < b, t, f)      |

| N×(s)     |                     |                                 |                         |

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

| Exp       | un_nx               | un_ex                           | $un_cx(t, f)$           |

|-----------|---------------------|---------------------------------|-------------------------|

| Ex(e)     | sxp(e)              | е                               | cjump(e $\neq$ 0, t, f) |

| Cx(a < b) | seq(sxp(a), sxp(b)) | $eseq(t \leftarrow (a < b), t)$ | cjump(a < b, t, f)      |

| N×(s)     | S                   |                                 |                         |

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

| Exp       | un_nx               | un_ex                           | $un_cx(t, f)$           |

|-----------|---------------------|---------------------------------|-------------------------|

| Ex(e)     | sxp(e)              | e                               | cjump(e $\neq$ 0, t, f) |

| Cx(a < b) | seq(sxp(a), sxp(b)) | $eseq(t \leftarrow (a < b), t)$ | cjump(a < b, t, f)      |

| N×(s)     | S                   | ???                             |                         |

Rather, delay the translation until the use is known (translate::Exp):

- Ex Expression shell, encapsulation of a proto value,

- Nx Statement shell, encapsulating a wannabe statement,

- Cx Condition shell, encapsulating a wannabe condition.

| Exp       | un_nx               | un_ex                           | $un_cx(t, f)$           |

|-----------|---------------------|---------------------------------|-------------------------|

| Ex(e)     | sxp(e)              | е                               | cjump(e $\neq$ 0, t, f) |

| Cx(a < b) | seq(sxp(a), sxp(b)) | $eseq(t \leftarrow (a < b), t)$ | cjump(a < b, t, f)      |

| N×(s)     | S                   | ???                             | ???                     |

#### if 11 < 22 | 22 < 33 then print\_int(1) else print\_int(0)

```

cjump ne

eseq seq cjump 11 < 22 name 10 name 11

label 10 move temp t0 const 1

jump name 12

label 11 move temp t0

eseq seq move temp t1 const 1

cjump 22 < 33 name 13 name 14

label 14

move temp t1 const 0

label 13

seq end

temp t1

jump name 12

label 12

seq end

temp t0

const 0

name 15

name 16

label 15 sxp call name print_int const 1

jump name 17

label 16

sxp call name print_int const 0

jump name 17

label 17

```

#### A Better Translation: Ix

```

seq

cjump 11 < 22 name 13 name 14

label 13

cjump 1 <> 0 name 10 name 11

label 14

cjump 22 < 33 name 10 name 11

seq end

label 10

sxp call name print_int const 1

jump name 12

label 11

sxp call name print_int const 0

label 12

```

# Complex Expressions

- Intermediate Representations

- 2 Memory Management

- 3 Translation to Intermediate Language

- Calling Conventions

- Clever Translations

- Complex Expressions

- The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

### Complex Expressions

- Array creation

- Record creation

- String comparison

- While loops

- For loops

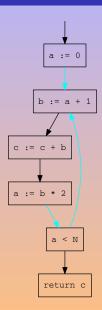

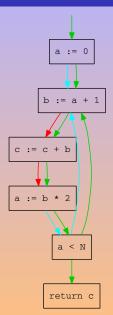

### While Loops

while condition do body

## While Loops

while condition do body

```

test:

if not (condition)

goto done

body

goto test

done:

```

### For Loops

```

for i := min to max

do body

```

```

let i := min

limit := max

in

while i <= limit

do

(body; ++i)

end</pre>

```

### For Loops

```

for i := min to max

do body

```

```

let i := min

limit := max

in

if (i > limit)

goto end

loop:

body

if (i >= limit)

goto end

++i

goto loop

end:

```

#### Additional Features

- Bounds checking

- Nil checking

- ..

# The Case of the Tiger Compiler

- Intermediate Representations

- 2 Memory Management

- 3 Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- Translation in the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

# Translation in the Tiger Compiler

- Intermediate Representations

- 2 Memory Management

- Translation to Intermediate Language

- 4 The Case of the Tiger Compiler

- Translation in the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

#### Actors: The temp Module

temp::Temp temporaries are pseudo-registers.

Generation of fresh temporaries.

temp::Label Pseudo addresses, both for data and code.

Generation of fresh labels.

misc::endo\_map<T> Mapping from T to T.

Used during register allocation.

#### Actors: The tree Module

#### Implementation of hir and lir.

```

/Tree/ /Exp/ Const (int)

Name

(temp::Label)

Temp (temp::Temp)

Binop (Oper, Exp, Exp)

Mem (Exp)

Call (Exp, list<Exp*>)

Eseq (Stm, Exp)

/Stm/

Move

(Exp, Exp)

Sxp

(Exp)

(Exp, list<temp::Label>)

Jump

CJump (Relop, Exp, Exp, Label, Label)

Seq

(list<Stm *>)

Label (temp::Label)

```

### Actors: The tree Module: Warnings

- temp::Temp is not tree::Temp.

The latter aggregates one of the former.

Similarly with Label.

- n-ary seq. (Unlike [Appel, 1998]).

- Sxp instead of Exp.

#### Actors: The frame Module

Access How to reach a "variable".

Abstract class with two concrete subclasses.

frame::In\_Register

frame::In\_Frame

Frame What "variables" a frame contains.

local\_alloc(bool escapes\_p) -> Access

Frames and (frame::) accesses are not aware of static links.

#### Actors: The translate Module

Access Static link aware version of frame::Access:

how to reach a variable, including non local: a frame::Access

and a translate::Level.

exp(Level use) -> Exp Tree expression

The location of this Access, from the use point of view.

Level Static link aware version of frame::Frame: what variables a frame contains, and where is its parent level.

fp(Level use) -> Exp Tree expression

The frame pointer of this Level, from the use point of view. Used for calls, and reaching frame resident temporaries.

#### Actors: The translate Module

translate::Exp

Prototranslation wrappers (Ex, Nx, Cx, Ix).

translate/translation.hh

Auxiliary functions used by the Translator.

translate::Translator

The translator.

## lir: Low Level Intermediate Representation

- Intermediate Representations

- 2 Memory Management

- Translation to Intermediate Language

- The Case of the Tiger Compiler

- 5 lir: Low Level Intermediate Representation

- Structure

No nested sequences.

- Expressions

Assembly is imperative: there is no "expression"

- Calling Conventions

A (high-level) call is a delicate operation, not a simple instruction.

- Machines provide "jump or continue" instructions.

- Limited Number of Registers

From temps to actual registers

- Structure

No nested sequences.

- Expressions

Assembly is imperative: there is no "expression".

- Calling Conventions

A (high-level) call is a delicate operation, not a simple instruction

- Two Way Conditional Jumps

Machines provide "jump or continue" instructions.

- Limited Number of Registers

From temps to actual registers.

- Structure

No nested sequences.

- Expressions

Assembly is imperative: there is no "expression".

- Calling Conventions

A (high-level) call is a delicate operation, not a simple instruction.

- Two Way Conditional Jumps

Machines provide "jump or continue" instructions

- Limited Number of Registers

From temps to actual registers

- Structure

No nested sequences.

- Expressions

Assembly is imperative: there is no "expression".

- Calling Conventions

A (high-level) call is a delicate operation, not a simple instruction.

- Two Way Conditional Jumps

Machines provide "jump or continue" instructions.

- Limited Number of Registers

From temps to actual registers

- Structure

No nested sequences.

- Expressions

Assembly is imperative: there is no "expression".

- Calling Conventions

A (high-level) call is a delicate operation, not a simple instruction.

- Two Way Conditional Jumps

Machines provide "jump or continue" instructions.

- Limited Number of Registers

From temps to actual registers.

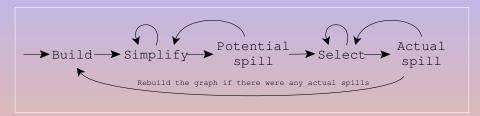

#### Linearization: Principle

- eseq and seq must be eliminated (except the outermost seq).

- Similar to cut-elimination: permute inner eseq and seq to lift them higher, until they vanish.

- A simple rewriting system.

```

eseq (s1, eseq (s2, e)) \rightarrow eseq (seq (s1, s2), e)

x (eseq (s, e)) \rightarrow seq (s, x (e))

```

seq (ss1, seq (ss2), ss3)  $\sim$  seq (ss1, ss2, ss3)

```

seq (ss1, seq (ss2), ss3) \sim seq (ss1, ss2, ss3) call (f, eseq (s, e), es)

```

```

seq (ss1, seq (ss2), ss3) \rightsquigarrow seq (ss1, ss2, ss3) call (f, eseq (s, e), es) \rightsquigarrow eseq (s, call (f, e, es))

```

```

seq (ss1, seq (ss2), ss3) \rightarrow seq (ss1, ss2, ss3) call (f, eseq (s, e), es) \rightarrow eseq (s, call (f, e, es)) binop (+, eseq (s, e1), e2)

```

```

seq (ss1, seq (ss2), ss3) \rightarrow seq (ss1, ss2, ss3)

call (f, eseq (s, e), es) \rightarrow eseq (s, call (f, e, es))

binop (+, eseq (s, e1), e2) \rightarrow eseq (s, binop (+, e1, e2))

```

```

seq (ss1, seq (ss2), ss3) \rightarrow seq (ss1, ss2, ss3)

call (f, eseq (s, e), es) \rightarrow eseq (s, call (f, e, es))

binop (+, eseq (s, e1), e2) \rightarrow eseq (s, binop (+, e1, e2))

binop (+, e1, eseq (s, e2))

```

```

seq (ss1, seq (ss2), ss3) \rightarrow seq (ss1, ss2, ss3)

call (f, eseq (s, e), es) \rightarrow eseq (s, call (f, e, es))

binop (+, eseq (s, e1), e2) \rightarrow eseq (s, binop (+, e1, e2))

binop (+, e1, eseq (s, e2)) \rightarrow eseq (s, binop (+, e1, e2))

```

- This transformation is invalid: it changes the semantics.

- How can it be solved?

```

binop (+, e1, eseq (s, e2)) \rightarrow eseq (s, binop (+, e1, e2))

```

• But what if s modifies the value of e1?

- This transformation is invalid: it changes the semantics.

- How can it be solved?

```

binop (+, e1, eseq (s, e2)) \rightarrow eseq (s, binop (+, e1, e2))

```

• But what if s modifies the value of e1?

- This transformation is invalid: it changes the semantics.

- How can it be solved?

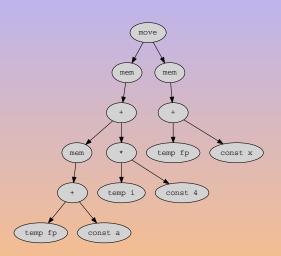

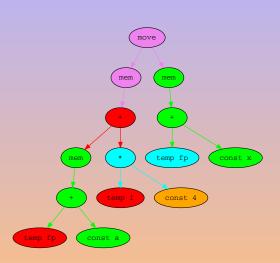

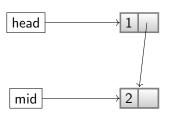

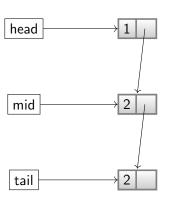

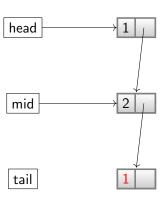

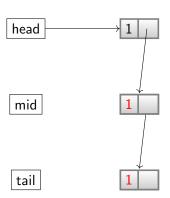

#### Wrong

#### Right

### Linearization: More Temporaries

When "de-expressioning" fresh temporaries are needed

More generally

This is extremely inefficient when not needed...

### Linearization: Commutativity

- Save useless extra temporaries and moves.

- Problem: commutativity cannot be known statically.

E.g., move (mem (t1), e) and mem (t2)

commute iff t1 \( \neq \) t2.

- We need a conservative approximation,

i.e., never say "commute" when they don't.

E.g., "if e is a const then s and e definitely commute".

### Linearization: Commutativity

- Save useless extra temporaries and moves.

- Problem: commutativity cannot be known statically.

E.g., move (mem (t1), e) and mem (t2)

commute iff t1 ≠ t2.

- We need a conservative approximation,

i.e., never say "commute" when they don't.

E.g., "if e is a const then s and e definitely commute".

### Linearization: Commutativity

- Save useless extra temporaries and moves.

- Problem: commutativity cannot be known statically.

E.g., move (mem (t1), e) and mem (t2)

commute iff t1 ≠ t2.

- We need a conservative approximation,

i.e., never say "commute" when they don't.

E.g., "if e is a const then s and e definitely commute".

#### Call Normalization

Normalization of a call depends on the kind of the routine:

procedure then its parent must be an sxp

function then its parent must be a move (temp t, .)

This normalization is performed simultaneously with linearization.

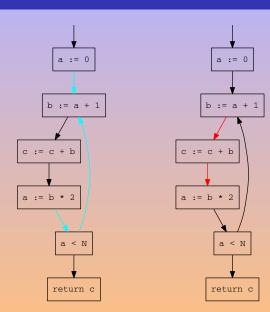

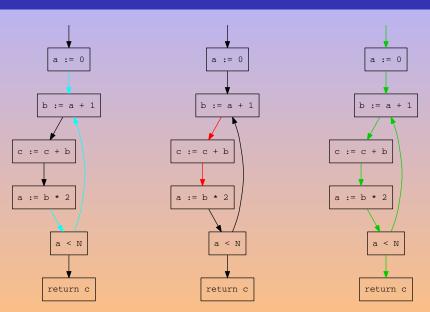

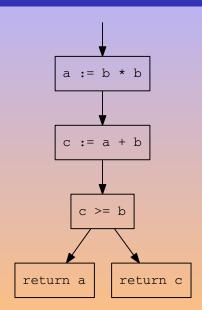

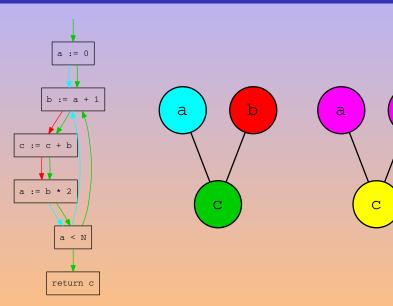

### Two Way Jumps

Obviously, to enable the translation of a cjump into actual assembly instructions, the "false" label must follow the cjump. How?

## Two Way Jumps: Basic Blocks

#### Split the long outer seq into "basic blocks":

- a single entry: the first instruction

- a single (maybe multi-) exit: the last instruction

#### It may require

- a new label as first instruction, to which the prologue jumps

- new labels after jumps or cjumps

- a new jump from the last instruction to the epilogue.

## Two Way Jumps: Traces

Start from the initial block, and "sew" each remaining basic block to this growing "trace".

- If the last instruction is a jump

- if the "destination block" is available, add it

- otherwise, fetch any other remaining block.

- If the last instruction is a cjump

- If the false destination is available, push it

- If the true destination is available, flip the cjump and push it,

- otherwise, change the cjump to go to a fresh label, attach this label, and finally jump to the initial false destination.

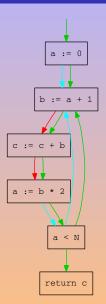

# Two Way Jumps: Optimizing Traces

Many jumps should be removable, but sometimes there are choices to make.

```

label prologue

Prologue.

jump name test

```

```

label test

cjump i <= N, body, done</pre>

```

```

label body

Body.

jump name test

```

```

label done

Epilogue

jump name end

```

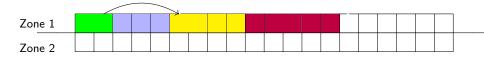

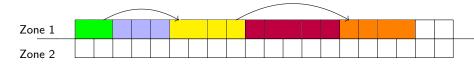

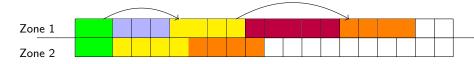

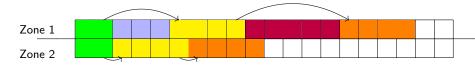

# Two Way Jumps: Optimizing Traces

label prologue

Prologue

jump name test

label prologue

Prologue

jump name test

label prologue

Prologue

jump name test

label test

cjump i > N,

done, body

label test

cjump i <= N,

body, done

label body *Body* jump name test

label body

Body

jump name test

label done

Epilogue

jump name end

label test

cjump i <= N,

body, done</pre>

label done

Epilogue

jump name end

label body

Body

jump name test

Epilogue

jump name end

# Two Way Jumps: Optimizing Traces

label prologue

Prologue

jump name test

label test

cjump i > N,

done, body

label body

Body

jump name test

label done

Epilogue

jump name end

label prologue

Prologue

jump name test

label test

cjump i <= N,

body, done</pre>

abel done

Epilogue

ump name end

abel body

Body

ump name test

label prologue

Prologue

jump name test

label body *Body* jump name test

cjump i <= N,

body, done</pre>

label done

Epilogue

jump name er

<ロ > ← □ > ← □ > ← □ > ← □ = ← の へ ○

# Two Way Jumps: Optimizing Traces

label prologue

Prologue

jump name test

label prologue

Prologue

jump name test

Prologue jump name

label test

cjump i > N,

done, body

label test

cjump i <= N,

body, done</pre>

label body

Body

jump name test

label done

Epilogue

jump name end

label done

Epilogue

jump name end

label body

Body

jump name test

label done

Epilogue

jump name e

<ロ > ← □ > ← □ > ← □ > ← □ = ← の へ ○

# Two Way Jumps: Optimizing Traces

label prologue

Prologue

jump name test

label prologue

Prologue

jump name test

label prologue

Prologue

jump name test

label test

cjump i > N,

done, body

label test

cjump i <= N,

body, done</pre>

label body

Body

jump name test

label body

Body

jump name test

label done

Epilogue

jump name end

label test

cjump i <= N,

body, done</pre>

label done

Epilogue

jump name end

label body

Body

jump name test

label done

Epilogue

jump name end

<ロ>

# Bibliography I

- Appel, A. W. (1998).

Modern Compiler Implementation in C, Java, ML.

Cambridge University Press.

- Edwards, S. (2003).

COMS W4115 Programming Languages and Translators.

http://www.cs.columbia.edu/~sedwards/classes/2003/w4115/.

larus, J. R. (1990).

SPIM S20: A MIPS R2000 simulator.

Technical Report TR966, Computer Sciences Department, University of Wisconsin–Madison.

# Bibliography II

Loosemore, S., Stallman, R. M., McGrath, R., Oram, A., and Drepper, U. (2003).

The GNU C Library Reference Manual.

Free Software Foundation, 59 Temple Place – Suite 330, Boston, MA 02111-1307 USA, 0.10 edition.

Muchnick, S. (1997).

Advanced Compiler Design and Implementation.

Morgan Kaufmann Publishers.

#### Instruction Selection

Akim Demaille Étienne Renault Roland Levillain first.last@lrde.epita.fr

EPITA — École Pour l'Informatique et les Techniques Avancées

April 23, 2018

#### Instruction Selection

- Microprocessors

- 2 A Typical risc: mips

- 3 The EPITA Tiger Compiler

- 4 Instruction Selection

- 5 Instruction Selection

# Microprocessors

- Microprocessors

- 2 A Typical risc: mips

- 3 The EPITA Tiger Compiler

- 4 Instruction Selection

- 5 Instruction Selection

Instruction set architecture is the structure of a computer that a machine language programmer (or a compiler) must understand to write a correct (timing independent) program for that machine IBM introducing 360 (1964)

The Instruction Set Architecture (ISA) is the part of the processor that is visible to the programmer or compiler writer.

#### What is an instruction set?

An instruction set specifies a processor functionality:

- what operations are supported

- what storage mechanisms are used

- how to access storage

- how to communicate program to processor

## Technical aspect of instruction set

- o format: length, encoding

- operations: data type (floating or fixed point), number and kind of operands

- 3 storage:

- internal: accumulator, stack, register

- memory: address size, addressing modes

- control: branch condition, support for procedures, predication

# What makes a good instruction set?

An instruction set specifies a processor functionnality:

- implementability: support for a (high performances) range of implementation

- programmability: easy to express program (by Humans before 80's, mostly by compiler nowadays)

- backward/forward compatibility: implementability & programmability across generation

### cisc - Complex Instruction Set Chip

- large number of instructions (100-250)

- 6, 8, 16 registers, some for pointers, others for integer computation

- arithmetic in memory can be processed

- two address code

- many possible effects (e.g., self-incrementation)

#### cisc - Pros & Cons

#### Pros:

- Simplified compiler: translation from IR is straightforward

- Smaller assembly code than risc assembly code

- Fewer instructions will be fetched

- Special purpose register available: stack pointer, interrupt handling ...

#### Cons:

- Variable length instruction format

- Many instruction require many clock for execution

- Limiter number of general purpose register

- (often) new version of cisc include the subset of instructions of the previous version

# Motivations for something else!

Though the CISC programs could be small in length, but number of bits of memory occupies may not be less

The complex instructions do not simplify the compilers: many clock cycles can be wasted to find the appropriate instruction.

risc architectures were designed with the goal of executing one instruction per clock cycle.

### risc - Reduced Instruction Set Chip

- 32 generic purpose registers

- arithmetic only available on registers

- 3 address code

- load and store relative to a register (M[r + const])

- only one effect or result per instruction

## risc – Pipeline 1/3

Pipelining is the overlapping the execution of several instructions in a pipeline fashion.

A pipeline is (typically) decomposed into five stages:

- Instruction Fetch (IF)

- 2 Instruction Decode (ID)

- Execute (EX)

- Memory Access (MA)

- Write Back (WB)

### risc – Pipeline 2/3

```

inst1:

IF

ID

EX

MA

WB

IF

inst2:

ID

EX

MA

WB

IF

inst3:

ID EX

MA

WB

inst4:

IF

ID EX

MA

WB

IF

ID

ΕX

inst5:

MA

WB

```

The slowest stage determines the speed of the whole pipeline!

#### Ex introduces latency

- Register-Register Operation: 1 cycle

- Memory Reference: 2 cycles

- Multi-cycle Instructions (floating point): many cycles

### risc – Pipeline 3/3

Data hazard: When an instruction depends on the results of a previous instruction still in the pipeline.

- inst1 write in \$s1 during WB

- inst1 read in \$s1 during ID

```

inst1: IF ID EX MA WB inst2: IF ID EX MA WB

```

inst2 must be split, causing delays...

other dependencies can appears

#### risc – Pros & Cons

#### Pros:

- Fixed length instructions: decoding is easier

- Simpler hardware: higher clock rate

- Efficient Instruction pipeline

- Large number of general purpose register

- Overlapped register windows to speed up procedure call and return

- One instruction per cycle

#### Cons:

- Minimal number of addressing modes: only Load and Store

- Relatively few instructions

# Nowadays

- the classification pure-risc or pure-cisc is becoming more and more inappropriate and may be irrelevant

- modern processors use a calculated combination elements of both design styles

- decisive factor is based on a tradeoff between the required improvement in performance and the expected added cost

- Some processors that are classified as CISC while employing a number of RISC features, such as pipelining

ARM provides the advantage of using a CISC (in terms of functionality) and the advantage of an RISC (in terms of reduced code lengths).

#### Lessons to be learned

### Implementability

Driven by technology: microcode, VLSI, FPGA, pipelining, superscalar, SIMD, SSE

#### Programmability

Driven by compiler technology

### Sum-up

- Many non technical issues influence ISA's

- Best solutions don't always win (Intel X86)

# Intel X86 (IA32)

- Introduced in 1978

- 8 × 32 bits "general" register

- variable length instructions (1–15 byte)

- long life to the king! 15 generations from Intel 8086 to Intel Kabylake

#### Intel's trick?

Decoder translates cisc into risc micro-operations

# A Typical risc: mips

- Microprocessors

- 2 A Typical risc: mips

- Integer Arithmetics

- Logical Operations

- Control Flow

- Loads and Stores

- Floating Point Operations

- 3 The EPITA Tiger Compiler

- Instruction Selection

- 5 Instruction Selection

# mips Registers and Use Convention [Larus, 1990]

| Name  | Number | Usage                                           |

|-------|--------|-------------------------------------------------|

| zero  | 0      | Constant 0                                      |

| at    | 1      | Reserved for assembler                          |

| v0-v1 | 2–3    | Expression evaluation and results of a function |

| a0-a3 | 4–7    | Function argument 1–4                           |

| t0-t7 | 8–15   | Temporary (not preserved across call)           |

| s0-s7 | 16–23  | Saved temporary (preserved across call)         |

| t8-t9 | 24–25  | Temporary (not preserved across call)           |

| k0-k1 | 26–27  | Reserved for OS kernel                          |

| gp    | 28     | Pointer to global area                          |

| sp    | 29     | Stack pointer                                   |

| fp    | 30     | Frame pointer                                   |

| ra    | 31     | Return address (used by function call)          |

# Typical risc Instructions

The following slides are based on [Larus, 1990].

- The assembler translates pseudo-instructions (marked with † below).

- In all instructions below, Src2 can be

- a register

- an immediate value (a 16 bit integer).

- The immediate forms are included for reference.

- The assembler translates the general form (e.g., add) into the immediate form (e.g., addi) if the second argument is constant.

# Integer Arithmetics

- Microprocessors

- 2 A Typical risc: mips

- Integer Arithmetics

- Logical Operations

- Control Flow

- Loads and Stores

- Floating Point Operations

- The EPITA Tiger Compiler

- 4 Instruction Selection

- 5 Instruction Selection

### Arithmetic: Addition/Subtraction

```

addi Rdest, Rsrc1, Imm

Addition Immediate (with overflow)

addu Rdest, Rsrc1, Src2

Addition (without overflow)

addiu Rdest, Rsrc1, Imm

Addition Immediate (without overflow)

Put the sum of the integers from Rsrc1 and Src2 (or Imm) into Rdest.

sub Rdest, Rsrc1, Src2

Subtract (with overflow)

subu Rdest, Rsrc1, Src2

Subtract (without overflow)

```

Put the difference of the integers from Rsrc1 and Src2 into Rdest.

Addition (with overflow)

add Rdest, Rsrc1, Src2

#### Arithmetic: Division

If an operand is negative, the remainder is unspecified by the mips architecture and depends on the conventions of the machine on which spim is run.

```

div Rsrc1, Rsrc2

divu Rsrc1, Rsrc2

```

Divide (signed)

Divide (unsigned)

Divide the contents of the two registers. Leave the quotient in register 10 and the

remainder in register hi.

Divide (signed, with overflow) †

div Rdest, Rsrc1, Src2

divu Rdest, Rsrc1, Src2

Divide (unsigned, without overflow) †

Put the quotient of the integers from Rsrc1 and Src2 into Rdest.

rem Rdest, Rsrc1, Src2

Remainder †

remu Rdest, Rsrc1, Src2

Unsigned Remainder †

Likewise for the the remainder of the division.

### Arithmetic: Multiplication

```

mul Rdest, Rsrc1, Src2

mulo Rdest, Rsrc1, Src2

mulou Rdest, Rsrc1, Src2

Multiply (with overflow) †

mulou Rdest, Rsrc1, Src2

Unsigned Multiply (with overflow) †

Put the product of the integers from Rsrc1 and Src2 into Rdest.

mult Rsrc1, Rsrc2

Multiply

multu Rsrc1, Rsrc2

Unsigned Multiply

Multiply the contents of the two registers. Leave the low-order word of the product in register 10 and the high-word in register hi.

```

#### Arithmetic Instructions

abs Rdest, Rsrc

Absolute Value †

Put the absolute value of the integer from Rsrc in Rdest.

Negate Value (with overflow) †

neg Rdest, Rsrc

Negate Value (with overflow) †

negu Rdest, Rsrc

Negate Value (without overflow) †

Put the negative of the integer from Rsrc into Rdest.

# Logical Operations

- Microprocessors

- 2 A Typical risc: mips

- Integer Arithmetics

- Logical Operations

- Control Flow

- Loads and Stores

- Floating Point Operations

- The EPITA Tiger Compiler

- 4 Instruction Selection

- Instruction Selection

### Logical Instructions

and Rdest, Rsrc1, Src2

andi Rdest, Rsrc1, Imm

**AND**

AND Immediate

Put the logical AND of the integers from Rsrc1 and Src2 (or Imm) into Rdest.

not Rdest, Rsrc

NOT †

Put the bitwise logical negation of the integer from Rsrc into Rdest.

### Logical Instructions

```

nor Rdest, Rsrc1, Src2

```

NOR

Put the logical NOR of the integers from Rsrc1 and Src2 into Rdest.

or Rdest, Rsrc1, Src2

OR

ori Rdest, Rsrc1, Imm

OR Immediate

Put the logical OR of the integers from Rsrc1 and Src2 (or Imm) into Rdest.

xor Rdest, Rsrc1, Src2

XOR

xori Rdest, Rsrc1, Imm

XOR Immediate

Put the logical XOR of the integers from Rsrc1 and Src2 (or Imm) into Rdest.

### Logical Instructions

```

rol Rdest, Rsrc1, Src2

Rotate Left †

Rotate Right †

ror Rdest, Rsrc1, Src2

Rotate the contents of Rsrc1 left (right) by the distance indicated by Src2 and

put the result in Rdest.

Shift Left Logical

sll Rdest, Rsrc1, Src2

Shift Left Logical Variable

sllv Rdest, Rsrc1, Rsrc2

Shift Right Arithmetic

sra Rdest, Rsrc1, Src2

srav Rdest, Rsrc1, Rsrc2

Shift Right Arithmetic Variable

Shift Right Logical

srl Rdest, Rsrc1, Src2

Shift Right Logical Variable

srlv Rdest, Rsrc1, Rsrc2

Shift the contents of Rsrc1 left (right) by the distance indicated by Src2

(Rsrc2) and put the result in Rdest.

```

### Control Flow

- Microprocessors

- 2 A Typical risc: mips

- Integer Arithmetics

- Logical Operations

- Control Flow

- Loads and Stores

- Floating Point Operations

- The EPITA Tiger Compiler

- 4 Instruction Selection

- Instruction Selection

### Comparison Instructions

seq Rdest, Rsrc1, Src2

Set Rdest to 1 if Rsrc1 equals Src2, otherwise to 0.

Set Equal †

sne Rdest, Rsrc1, Src2

Set Not Equal †

Set Rdest to 1 if Rsrc1 is not equal to Src2, otherwise to 0.

### Comparison Instructions

```

Set Greater Than Equal †

sge Rdest, Rsrc1, Src2

Set Greater Than Equal Unsigned †

sgeu Rdest, Rsrc1, Src2

Set Rdest to 1 if Rsrc1 \geq Src2, otherwise to 0.

Set Greater Than †

sgt Rdest, Rsrc1, Src2

Set Greater Than Unsigned †

sgtu Rdest, Rsrc1, Src2

Set Rdest to 1 if Rsrc1 > Src2, otherwise to 0.

Set Less Than Equal †

sle Rdest, Rsrc1, Src2

sleu Rdest, Rsrc1, Src2

Set Less Than Equal Unsigned †

Set Rdest to 1 if Rsrc1 < Src2, otherwise to 0.

Set Less Than

slt Rdest, Rsrc1, Src2

Set Less Than Immediate

slti Rdest, Rsrc1, Imm

Set Less Than Unsigned

sltu Rdest, Rsrc1, Src2

Set Less Than Unsigned Immediate

sltiu Rdest, Rsrc1, Imm

Set Rdest to 1 if Rsrc1 < Src2 (or Imm), otherwise to 0.

```

Branch instructions use a signed 16-bit offset field: jump from  $-2^{15}$  to  $+2^{15}-1$ ) instructions (not bytes). The jump instruction contains a 26 bit address field.

b label Branch instruction †

Unconditionally branch to label.

j label Jump

Unconditionally jump to label.

jal labelJump and Linkjalr RsrcJump and Link Register

Unconditionally jump to *label* or whose address is in Rsrc. Save the address of the next instruction in register 31.

jr Rsrc Jump Register

Unconditionally jump to the instruction whose address is in register Rsrc.

bczt label Branch Coprocessor z True

bczf label Branch Coprocessor z False

Conditionally branch to label if coprocessor z's condition flag is true (false).

Conditionally branch to *label* if the contents of Rsrc1 \* Src2.

```

beq Rsrc1, Src2, label

bne Rsrc1, Src2, label

```

begz Rsrc, label

bnez Rsrc, label

Branch on Equal Branch on Not Equal

Branch on Equal Zero † Branch on Not Equal Zero †

Conditionally branch to *label* if the contents of Rsrc1 \* Src2.

bge Rsrc1, Src2, label

Branch on Greater Than Equal †